File:5 Stage Pipeline.svg

此SVG文件的PNG预览的大小:300 × 190像素。 其他分辨率:320 × 203像素 | 640 × 405像素 | 1,024 × 649像素 | 1,280 × 811像素 | 2,560 × 1,621像素。

原始文件 (SVG文件,尺寸为300 × 190像素,文件大小:33 KB)

文件历史

点击某个日期/时间查看对应时刻的文件。

| 日期/时间 | 缩略图 | 大小 | 用户 | 备注 | |

|---|---|---|---|---|---|

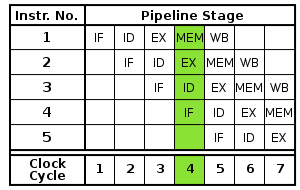

| 当前 | 2009年1月22日 (四) 18:24 |  | 300 × 190(33 KB) | Inductiveload | {{Information |Description={{en|1=A diagram showing the stage of execution reached by five consecutive instructions in a 5-stage microprocessor. At clock cycle 4, the 1st instruction is in the "memory access" phase, the second is in the "execute" phase, t |

文件用途

以下页面使用本文件:

全域文件用途

以下其他wiki使用此文件:

- en.wikibooks.org上的用途

- et.wikipedia.org上的用途

- ja.wikipedia.org上的用途

- no.wikipedia.org上的用途