哈佛架構

| 此條目沒有列出任何參考或來源。 (2019年6月14日) |

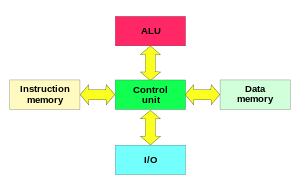

哈佛架構(英語:Harvard architecture)是一種將程式指令儲存和數據儲存分開的記憶體結構(Split Cache)。這一詞起源於Harvard Mark I型繼電器式電腦,它儲存指令(24位元)在紙帶上和數據於機電計數器上。 中央處理器首先到程式指令儲存器中讀取程式指令內容,解碼後得到數據地址,再到相應的數據儲存器中讀取數據,並進行下一步的操作(通常是執行)。程式指令儲存和數據儲存分開,數據和指令的儲存可以同時進行,可以使指令和數據有不同的數據寬度,如Microchip公司的PIC16晶片的程式指令是14位元寬度,而數據是8位元寬度。程式需要由操作者載入;處理器無法自行初始化。

如今,大多數處理器由於效能原因實現了這種獨立訊號通路的結構,但實際上大多是應用了改進的哈佛結構,所以它們可以支援從磁碟將一個程式作為數據載入並執行的任務。

哈佛架構的微處理器通常具有較高的執行效率。其程式指令和數據指令分開組織和儲存的,執行時可以預先讀取下一條指令。

目前使用哈佛架構的中央處理器和微控制器有很多,除了上面提到的Microchip公司的PIC系列晶片,還有摩托羅拉公司的MC68系列、Zilog公司的Z8系列、Atmel公司的AVR系列和安謀公司的ARM9、ARM10和ARM11。

內存的詳細資訊

編輯在哈佛架構,兩個暫存器不需要有共同的特徵。特別是,字寬、定時、實現技術和內存地址都可以不同。在一些系統中,指令可以儲存在唯讀記憶體(ROM)中,而數據記憶體一般需要讀寫記憶體(RAM等)。在一些系統中,指令記憶體比數據記憶體多,因此指令地址比數據地址更寬。

與馮紐曼架構的對比

編輯純馮紐曼架構下的CPU可以讀取指令或讀/寫內存數據,它們都不能使指令和數據同時使用同一個的匯流排系統。使用哈佛結構的電腦中CPU,即使沒有緩衝記憶體的情況下也可以在讀取指令的同時進行數據訪問。由於指令和數據訪問不使用同一個內存通道,因此哈佛結構的電腦可以在相同的電路複雜度下有更好的表現。

同時,哈佛架構機擁有不同的代碼和數據的地址空間:指令的零地址和數據的零地址是不同的。指令的零地址可能是二十四位的值,而數據的零地址可能是一個八位位元組,而非二十四位值的一部分。

與改進的哈佛架構的對比

編輯改進的哈佛架構機與原來的哈佛架構機並無兩樣,但它鬆綁了指令和數據之間嚴格分離的這一特徵,仍然允許CPU同時訪問兩個(或更多)內存匯流排。最常見的修改包括由公共地址空間支援的單獨指令和數據緩衝記憶體。當它作為一個純粹的哈佛機時,CPU通過緩衝記憶體來執行指令。當訪問外部記憶體時,它的作用就像一個馮·諾依曼機(代碼可以像數據一樣移動,像是一個功能強大的技能)。這一改良在現代處理器是普遍存在的,例如ARM體系結構、Power Architecture和x86處理器。它有時被稱為哈佛架構,忽略了它實際上被「修改」的事實。

另一種修改提供了指令記憶體(例如ROM或快閃記憶體)與CPU之間的通路,以允許來自指令記憶體的字被視為唯讀數據。該技術用於某些微控制器,包括Atmel的AVR。這允許訪問諸如文字字串或函數表之類的常數數據,而無需首先將其複製到數據記憶體中,從而為讀/寫變數保留稀缺(且耗電的)數據記憶體。特殊的機器語言指令提供了從指令記憶體中讀取數據的功能。(這是不同於指令本身嵌入常數的數據,雖然對於單個常數來說,兩種機制可以相互替代。)

速度

編輯近年來,CPU的速度已經提速了許多次以同步主記憶體的存取速度。要注意減少內存訪問次數的數量以保持效能。例如,每一個指令在CPU執行需要訪問內存,增加電腦CPU沒有任何速度提升的問題叫做內存限制。可能使內存非常快,但由於內存成本,電源和訊號路由的原因這類內存數目很少。解決的辦法是提供少量的快速記憶體稱為CPU緩衝記憶體以存放最近訪問過的數據。CPU提取緩衝記憶體中的數據速度要比緩衝記憶體提取主要暫存器數據的速度更快。

內部與外部的設計

編輯現代高效能CPU晶片在設計上包含了哈佛和馮紐曼結構的特點。特別是,「拆分緩衝記憶體」這種改進型的哈佛架構版本是很常見的。 CPU的緩衝記憶體分為指令緩衝記憶體和數據緩衝記憶體。CPU訪問緩衝記憶體時使用哈佛體系結構。然而當緩衝記憶體未命中時,數據從主記憶體中檢索,卻並不分為獨立的指令和數據部分,雖然它有獨立的內存控制器用於訪問RAM,ROM和(NOR)快閃記憶體。 因此,在一些情況下可以看到馮紐曼架構,比如當數據和代碼通過相同的內存控制器時,這種硬件通過哈佛架構在緩衝記憶體訪問或至少主內存訪問方面提高了執行效率。 此外,在寫非緩衝記憶體區之後,CPU經常擁有寫緩衝記憶體使CPU可以繼續執行。當指令被CPU當作數據寫入,且軟件必須確保在試圖執行這些剛寫入的指令之前,緩衝記憶體(指令和數據)和寫緩衝記憶體是同步的,這時馮紐曼結構的內存特點就出現了。

哈佛結構的現代應用

編輯純粹的哈佛架構同時訪問多個儲存系統的主要優點是由哈佛處理器利用現代CPU緩衝記憶體系統。相對純的哈佛架構機主要用於在應用中的取捨,就像忽略緩衝記憶體的成本和節省功率,大於編程在不同的代碼和數據的地址空間的不利。

- 數碼訊號處理器(DSPs) 一般執行少,高度最佳化的音頻或影片處理演算法。他們避免緩衝記憶體,因為他們的行為必須非常重現。應對多地址空間的困難,執行速度是次要的問題。因此,一些DSP功能在不同的地址空間的多個數據記憶體便於SIMD和VLIW處理。德克薩斯儀器TMS320 C55x處理器,具有多個並列數據匯流排(雙寫,三讀)和指令匯流排。

- 單晶片的特點是具有少量的程式(快閃記憶體)、數據記憶體(SRAM),沒有緩衝記憶體,並利用哈佛架構的並列高速處理指令和數據的訪問。分開儲存的程式和數據記憶體可能具有不同的位寬,例如使用16位元指令和8位元寬的數據。這也意味着指令預取可以與其他活動同時進行。例子包括,Atmel的AVR和Microchip的 PIC。

即使在這種情況下,它是為了訪問程式記憶體唯讀表的數據使用特殊指令或重新編程;這些處理器是改進的哈佛架構的處理器。