中央處理器

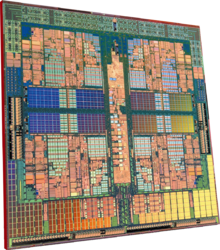

CPU(中國大陸作中央處理器,台灣作CPU)(英語:Central Processing Unit,英文縮寫為CPU)是電腦的主要裝置之一,功能主要是解釋電腦指令以及處理電腦軟件中的數據。1970年代以前,中央處理器由多個獨立單元構成,後來發展出由集成電路製造的中央處理器,這些高度收縮的元件就是所謂的微處理器,其中分出的中央處理器最為複雜的電路可以做成單一微小功能強大的單元,也就是所謂的核心。

| 此條目使用外部連結的方式可能不符合維基百科的方針或指引,或致使內文成為連結農場。 (2020年1月7日) |

中央處理器廣義上指一系列可以執行複雜的電腦程式的邏輯機器。這個空泛的定義很容易地將在「CPU」這個名稱被普遍使用之前的早期電腦也包括在內。無論如何,至少從1960年代早期開始,這個名稱及其縮寫已開始在電腦產業中得到廣泛應用。儘管與早期相比,「中央處理器」在物理形態、設計製造和具體任務的執行上有了極大的發展,但是其基本的操作原理一直沒有改變。

早期的中央處理器通常是為大型及特定應用的電腦而客製化。但是,這種昂貴的為特定應用客製化CPU的方法很大程度上已經讓位於開發便宜、標準化、適用於一個或多個目的的處理器類。這個標準化趨勢始於由單個電晶體組成的大型電腦和微機年代,隨着集成電路的出現而加速。IC使得更為複雜的中央處理器可以在很小的空間中設計和製造(在微米的數量級)。中央處理器的標準化和小型化都使這一類電子零件在現代生活中的普及程度越來越高。現代處理器出現在包括從汽車、手機到兒童玩具在內的各種物品中。

歷史

編輯在現今的CPU出現之前,如同ENIAC之類的電腦在執行不同程式時,必須經過一番線路調整才能啟動。由於它們的線路必須被重設才能執行不同的程式,這些機器通常稱為「固定程式電腦」(fixed-program computer)。而由於CPU這個詞指稱為執行軟件(電腦程式)的裝置,那些最早與儲存程式型電腦一同登場的裝置也可以被稱為CPU。

儲存程式型電腦的主意早已體現在ENIAC的設計上,但最終還是被省略以期早日完成。在1945年6月30日,ENIAC完成之前,著名數學家馮·諾伊曼發表名為《關於EDVAC的報告草案》的論文。它揭述儲存程式型電腦的計劃將在1949年8月完成。[1]EDVAC的目標是執行一定數量與種類的指令(或操作),這些指令結合產生出可以讓EDVAC執行的有用程式。特別的是,為EDVAC而寫的程式是儲存在高速電腦內存中,而非由實體線路組合而成。這項設計克服了ENIAC的某些局限——即花費大量時間與精力重設線路以執行新程式。在馮·諾伊曼的設計下,EDVAC可以藉由改變內儲存存的內容,簡單更換它執行的程式(軟件)[註 1]。

值得注意的是,儘管馮·諾伊曼由於設計了EDVAC,使得他在發展儲存程式型電腦上的貢獻最為顯著,但其他早於他的研究員如康拉德·楚澤(Konard Zuse)也提出過類似的想法。另外早於EDVAC完成,利用哈佛架構製造的馬克一號,也利用打孔帶而非電子內存用作儲存程式的概念。馮·諾伊曼架構與哈佛架構最主要的不同在於後者將CPU指令與資料分開存放與處置,而前者使用相同的內存位置。大多近代的CPU依照馮·諾伊曼架構設計,但哈佛架構一樣常見。

身為數碼裝置,所有CPU處理不連續狀態,因此需要一些轉換與區分這些狀態的基礎元件。在市場接受電晶體前,繼電器與真空管常用在這些用途上。雖然這些材料速度上遠優於純粹的機械構造,但是它們有許多不可靠的地方。例如以繼電器建造直流序向邏輯迴路需要額外的硬件以應付接觸點跳動問題。而真空管不會有接觸點跳動問題,但它們必須在啟用前預熱,也必須同時停止運作[註 2]。通常當一根真空管壞了,CPU必須找出損壞元件以置換新管。因此早期的電子真空管式電腦快於電子繼電器式電腦,但維修不便。類似EDVAC的真空管電腦每隔八小時便會損壞一次,而較慢較早期的馬克一號卻不太發生故障。[2]但在最後,由於速度優勢,真空管電腦主宰了當時的電腦世界,儘管它們需要較多的維護照顧。大多早期的同步CPU,其時脈頻率低於近代的微電子設計(見下列對於時脈頻率的討論)。那時常見的時脈頻率為10萬赫茲到4百萬赫茲,大大受限於內建切換裝置的速度。

分立電晶體與集成電路中央處理器

編輯由於許多科技廠家投入更小更可靠的電子裝置,使得設計CPU變得越來越複雜。電晶體的面世即是CPU第一個質的飛躍。1950到60年代的電晶體CPU不再以體積龐大、不可靠與易碎的開關元件(例如繼電器與真空管)建造。藉由這項改良,更加複雜與可靠的CPU便被建造在一個或多個包含分立(離散)元件的印刷電路板上,從而向體積小、可靠與不易損壞方向發展。

在此時期,將許多電晶體放置在擁擠空間中的方法大為普及。集成電路(IC)將大量的電晶體集中在一小塊半導體片,或晶片(chip)上。剛開始只有非常基本、非特定用途的數碼電路小型化到IC上(例如NOR邏輯閘)。以這些預裝式IC為基礎的CPU稱為小規模集成電路(SSI)裝置。SSI IC,例如裝置在阿波羅導航電腦上的那些電腦,通常包含數十個電晶體。以SSI IC建構整個CPU需要數千個獨立的晶片,但與之前的分立電晶體設計相比,依然省下很多空間與電力。肇因於微電子科技的進步,在IC上的電晶體數量越來越大,因此減少了建構一個完整CPU需要的獨立IC數量。「中規模集成電路」(MSI)與「大規模集成電路」(LSI)將內含的電晶體數量增加到成百上千。

1964年IBM推出了System/360電腦架構,此架構讓一系列速度與效能不同的IBM電腦可以執行相同的程式。此確實為一項創舉,因為當時的電腦大多互不相容,甚至同一家廠商製造的也是如此。為了實踐此項創舉,IBM提出了微程式概念,此概念依然廣泛使用在現代CPU上。[3]System/360架構由於太過成功,因此主宰了大型電腦數十年之久,並留下一系列使用相似架構,名為IBM zSeries的現代主機產品。同一年(1964),迪吉多(DEC)推出另一個深具影響力且瞄準科學與研究市場的電腦,名為PDP-8。DEC稍後推出非常有名的PDP-11,此產品原先計劃以SSI IC構組,但在LSI技術成熟後改為LSI IC。與之前SSI和MSI的祖先相比,PDP-11的第一個LSI產品包含了一個只用了4個LSI IC的CPU。[4]

電晶體電腦有許多前一代產品沒有的優點。除了可靠度與低耗電量之外,由於電晶體的狀態轉換時間比繼電器和真空管短得多,CPU也就擁有更快的速度。得益於可靠度的提升和電晶體轉換器切換時間的縮短,CPU的時脈頻率在此時期達到十幾百萬赫茲。另外,由於分立電晶體與IC CPU的使用量大增,新的高效能設計,例如SIMD(單指令多數據)、向量處理機開始出現。這些早期的實驗性設計,刺激了之後超級電腦(例如克雷公司)的崛起。

中央處理器操作原理

編輯CPU的主要運作原理,不論其外觀,都是執行儲存於被稱為程式裏的一系列指令。在此討論的是遵循普遍的馮·諾伊曼結構(von Neumann architecture)設計的裝置。程式以一系列數碼儲存在電腦記憶體中。差不多所有的馮·諾伊曼CPU的運作原理可分為四個階段:提取、解碼、執行和寫回。

第一階段,提取,從程式內存中檢索指令(為數值或一系列數值)。由程式計數器指定程式記憶體的位置,程式計數器儲存供識別目前程式位置的數值。換言之,程式計數器記錄了CPU在目前程式裏的蹤跡。提取指令之後,PC根據指令式長度增加記憶體單元[註 3]。指令的提取常常必須從相對較慢的記憶體尋找,導致CPU等候指令的送入。這個問題主要被論及在現代處理器的緩衝記憶體和管線化架構(見下)。

CPU根據從記憶體提取到的指令來決定其執行行為。在解碼階段,指令被拆解為有意義的片段。根據CPU的指令集架構(ISA)定義將數值解譯為指令[註 4]。一部分的指令數值為運算碼,其指示要進行哪些運算。其它的數值通常供給指令必要的資訊,諸如一個加法運算的運算目標。這樣的運算目標也許提供一個常數值(即立即值),或是一個空間的定址值:暫存器或記憶體地址,以定址模式決定。在舊的設計中,CPU裏的指令解碼部分是無法改變的硬體裝置。不過在眾多抽象且複雜的CPU和ISA中,一個微程式時常用來幫助轉換指令為各種形態的訊號。這些微程式在已成品的CPU中往往可以重寫,方便變更解碼指令。

在提取和解碼階段之後,接着進入執行階段。該階段中,連接到各種能夠進行所需運算的CPU部件。例如,要求一個加法運算,算術邏輯單元將會連接到一組輸入和一組輸出。輸入提供了要相加的數值,而且在輸出將含有總和結果。ALU內含電路系統,以於輸出端完成簡單的普通運算和邏輯運算(比如加法和位元運算)。如果加法運算產生一個對該CPU處理而言過大的結果,在標誌暫存器裏,溢位標誌可能會被設置(參見以下的數值精度探討)。

最終階段,寫回,以一定格式將執行階段的結果簡單的寫回。運算結果經常被寫進CPU內部的暫存器,以供隨後指令快速存取。在其它案例中,運算結果可能寫進速度較慢,如容量較大且較便宜的主記憶體。某些類型的指令會操作程式計數器,而不直接產生結果資料。這些一般稱作「跳轉」並在程式中帶來循環行為、條件性執行(透過條件跳轉)和函數[註 5]。許多指令也會改變標誌暫存器的狀態位元。這些標誌可用來影響程式行為,緣由於它們時常顯出各種運算結果。例如,以一個「比較」指令判斷兩個值的大小,根據比較結果在標誌暫存器上設置一個數值。這個標誌可藉由隨後的跳轉指令來決定程式動向。

在執行指令並寫回結果資料之後,程式計數器的值會遞增,反覆整個過程,下一個指令周期正常的提取下一個順序指令。如果完成的是跳轉指令,程式計數器將會修改成跳轉到的指令地址,且程式繼續正常執行。許多複雜的CPU可以一次提取多個指令、解碼,並且同時執行。這個部分一般涉及「經典RISC管線化」,那些實際上是在眾多使用簡單CPU的電子裝置中快速普及(常稱為微控制器)[註 6]。

設計與實作

編輯整數範圍

編輯CPU數碼表示方法是一個設計上的選擇,這個選擇影響了裝置的工作方式。一些早期的數碼電腦內部使用電氣模型來表示通用的十進制(基於10進位)記數系統數碼。還有一些罕見的電腦使用三進制表示數碼。幾乎所有的現代的CPU使用二進制系統來表示數碼,這樣數碼可以用具有兩個值的物理量來表示,例如高低電平[註 7]等等。

與數表示相關的是一個CPU可以表示的數的大小和精度,在二進制CPU情形下,一個位(bit)指的是CPU處理的數中的一個有意義的位,CPU用來表示數的位數量常常被稱作「字長」、「位寬」、「數據通路寬度」,或者當嚴格地涉及到整數(與此相對的是浮點數)時,稱作「整數精度」,該數量因體系結構而異,且常常在完全相同的CPU的不同部件中也有所不同。例如:一個8位元的CPU可處理在八個二進制數碼(每個數碼具有兩個可能的取值,0或1)表示範圍內的數,也就是說,28或256個離散的數值。 實際上,整數精度在CPU可執行的軟件所能利用的整數取值範圍上設置了硬件限制。[註 8]

整數精度也可影響到CPU可定址(定址)的內存數量。譬如,如果二進制的CPU使用32位來表示內存地址,而每一個內存地址代表一個八位元組,CPU可定位的容量便是232個位元組或4GB。以上是簡單描述的CPU地址空間,通常實際的CPU設計使用更為複雜的定址方法,例如為了以同樣的整數精度定址更多的內存而使用分頁技術。

更高的整數精度需要更多線路以支援更多的數碼位元,也因此結構更複雜、更巨大、更花費能源,也通常更昂貴。因此儘管市面上有許多更高精準度的CPU(如16,32,64甚至128位元),但依然可見應用軟件執行在4或8位元的微控制器上。越簡單的微控制器通常較便宜,花費較少能源,也因此產生較少熱量。這些都是設計電子裝置的主要考量。然而,在專業級的應用上,額外的精度給予的效益(大多是給予額外的地址空間)通常顯著影響它們的設計。為了同時得到高與低位寬度的優點,許多CPU依照不同功用將各部分設計成不一樣的位寬度。例如IBM System/370使用一個原為32位元的CPU,但它在其浮點單元使用了128位元精度,以得到更佳的精確度與浮點數的表示範圍。[3]許多後來的CPU設計使用類似的混合位寬,尤其當處理器設計為通用用途,因而需要合理的整數與浮點數運算能力時。

時脈頻率

編輯主頻=外頻×倍頻。

大部分的CPU,甚至大部分的序向邏輯裝置,本質上都是同步的。[註 9]也就是說,它們被設計和使用的前題是假設都在同一個同步訊號中工作。這個訊號,就是眾所周知的時脈訊號,通常是由一個周期性的方波(構成)。通過計算電訊號在CPU眾多不同電路中的分支中迴圈所需要的最大時間,設計者們可為時脈訊號選擇一個適合的周期。

該周期必須比訊號在延遲最大的情況下移動或者傳播所需的時間更長。設計整個CPU在時脈訊號的上升沿和下降沿附近流動數據是可能的。無論是在設計還是元件的維度看來,均對簡化CPU有顯著的優點。同時,它也存在CPU必須等候回應較慢元件的缺點。此限制已透過多種增加CPU並列運算的方法下被大幅的補償了。(見下文)

無論如何,結構上的改良無法解決所有同步CPU的弊病。比方說,時脈訊號易受其它的電子訊號影響。在逐漸複雜的CPU中,越來越高的時脈頻率使其更難與整個單元的時脈訊號同步。是故近代的CPU傾向發展多個相同的時脈訊號,以避免單一訊號的延遲使得整個CPU失靈。另一個主要的問題是,時脈訊號的增加亦使得CPU產生的熱能增加。持續變動的時脈頻率使得許多元件切換(Switch)而不論它們是否處於運作狀態。一般來說,一個處於切換狀態的元件比處於靜止狀態還要耗費更多的能源。因此,時脈頻率的增加使得CPU需要更有效率的冷卻方案。

其中一個處理切換不必要元件的方法稱為時脈閘控,即關閉對不必要元件的時脈頻率(有效的禁止元件)。但此法被認為太難實行而不見其低耗能通用性。[註 10]另一個對全程時脈訊號的方法是同時移除時脈訊號。當移除全程時脈訊號;使得設計的程式更加複雜時,非同步(或無時脈)設計使其在能源消耗與產生熱能的維度上更有優勢。罕見的是,所有的CPU建造在沒有利用全程時脈訊號的狀況。兩個值得注意的範例是ARM("Advanced RISC Machine")順從AMULET以及MIPS R3000相容MiniMIPS。與其完全移除時脈訊號,部份CPU的設計允許一定比例的裝置不同步,比方說使用不同步算術邏輯單元連接超純量管線化以達成一部份的算術效能增進。在不將時脈訊號完全移除的情況下,不同步的設計可使其表現出比同步計數器更少的數學運算。因此,結合了不同步設計極佳的能源耗損量及熱能產生率,使它更適合在嵌入式電腦上運作。[5]

並列

編輯前面描述的CPU結構只能在同一時間點執行一個指令,這種類型的CPU被稱為低純量。

這一類型的CPU有一很大的缺點:效率低。由於只能執行一個指令,此類的行程給與低純量CPU原生的低效能。由於每次僅有一個指令能夠被執行,CPU必須等到上個指令完成才能繼續執行。如此便造成下純量CPU延宕在需要兩個以上的時鐘循環才能完成的指令。即便增加第二個執行單元(見下文)也不會大幅提升效能;除了單一通道的延宕以外,雙通道的延宕及未使用的電晶體數量亦增加了。如此的設計使得不論CPU可使用的資源有多少,都僅能一次執行一個指令並可能達到純量的效能(一個指令需一個時脈循環)。無論如何,大部份的效能均為下純量(一個指令需超過一個時脈循環)。

為了達成純量目標以及更佳的效能,導致使得CPU傾向平行運算的各種設計越來越多。提到CPU的平行,有兩個字彙常用來區分這些設計的技術。指令平行處理(Instruction Level Parallelism, ILP)以增加CPU執行指令的速率(換句話說,增加on-die執行資源的利用),以及執行緒平行處理(Thread Level Parallelism, TLP)目的在增加執行緒(有效的個別程式)使得CPU可以同時執行。每種方法均可由其如何嵌入或相對有效(對CPU的效能)來區分。[註 11]

- 指令級並行(Instruction level parallelism,ILP):指令管線化與超純量架構

其中一種達成增加平行運算的方法,便是在主要指令完成執行之前,便進行指令提取及解碼。這種最簡易的技術,我們稱為指令管線化,且其被利用在泰半現代的泛用CPU中。透過分解執行通道至離散階段,指令管線化可以兩個以上的指令同時執行。相較於已被淘汰的組合管線化,指令管線化不再使用等候指令完全在管線化中退出才執行下一指令的技術。

指令管線化產生了下一作業需要前一作業才可完成的可能性。此類狀況又常稱為相依衝突。解決的方法是,對此類的情況增加額外的注意,及在相依衝突發生時延遲一部份的指令。自然地,此種解決方法需要額外的循環,是故指令管線化的處理器比低純量處理器還要複雜。(雖然不是很顯著)一個指令管線化的處理器的效能可能十分接近純量,只需禁止管線化推遲即可。(在一個階段需要超過一個以上的循環的指令)

此外,對於指令管線化的改進啟發了減少CPU元件閒置時間的技術。稱為超純量的設計包括了一條長指令管線化及多個相同的執行單元。上純量管線化的分派器同時讀取及通過數個指令;分派器決定指令是否能夠平行執行(同時執行)並分配到可執行的執行單元。大致上來說,一個上純量的CPU能夠同時分派越多的指令給閒置的執行單元,就能夠完成越多的指令。

上純量CPU結構的設計中,最困難的部份便是創造一個有效率的分派器。分派器必須能夠快速且正確的決定指令是否能夠平行執行,並且讓閒置的執行單元最小化。其需要指令管線化常時的充滿指令流,且提升了在上純量結構中一定數量的CPU緩衝記憶體。其亦催生了危害迴避的技術,如分支預測、投機執行與跨序執行以維持高層次的效能。藉由嘗試預測特定的指令選擇何分支(路徑),CPU能夠最小化整個指令管線化等待特定的指令完成的次數。投機執行則是藉着執行部份的指令以得知其是否在整個作業完成後仍被需要而提供適度的效能提升。跨序執行則是重新整理指令執行的命令以降低資料相依。

當不是所有的CPU元件均有上純量效能時,未達上純量的元件效能便會因定序推遲而降低。奔騰的原型有兩個每一時脈循環可接收一個指令的上純量算術邏輯單元,但其浮點算術處理器(Floating Point Unit, FPU)不能在每一時脈循環接收一個指令。因此P5的效能只能算是整數上純量而非浮點上純量。英特爾Pentium結構的下一代P6加入了浮點運算處理器的上純量能力,因此在浮點指令上有顯著的效能提升。

此兩種簡單的管線化及上純量設計,均能透過允許單一處理器在一個時鐘迴圈完成一個指令[註 12],提升指令管線化的效能。多數的近代CPU設計至少都在上純量以上,且幾乎所有十年內的泛用CPU均達上純量。近年來,一些重視高指令管線化的電腦將其從CPU的硬體移至軟件。超長指令字元(的策略使得一部份的指令管線化成為軟件,減少CPU推動指令管線化的工作量,並降低了CPU的設計複雜度。

- 線程級並行(Thread-level parallelism,TLP):同時執行緒執行或線程級並列處理

另一個常用以增加CPU平行運算效能的策略是讓CPU有同時執行多個執行緒的能力。大致上說來,高同時執行緒平行執行(TLP)CPU比高指令平行執行來的有用。許多由克雷公司(Cray)公司於1970年代及1980年代晚期所首創的同時執行緒平行執行,專於該方法而啟發了龐大的計算效力。(就時間上而言)事實上,TLP多線程運算自從1950年就已經開始被運用了(Smotherman 2005)。在單處理器設計中,兩種主要實現TLP的設計方法是晶片級多處理(CMP)晶片層多線程處理和同步多線程(simultaneous multithreading,SMT)。同級別層多線程處理。在更進階層中,一台電腦中有多個單獨的處理器,常常運用對稱多處理機(SMP)和non-uniform memory access(NUMA)非獨立內存訪問的方式來組織。[註 13]這些非常不同的方法,全部為了實現同一個目標,就是增加CPU同時處理多個線程的能力。

CMP和SMP這兩種方法其實是非常相似的,而且是最直接的方法。這裏有一些概念上的東西關於如何實兩個或是兩個以上完全單獨的CPU。在CMP中,多個處理器內核會被放入同一個包中,有時會在非常相近的集成電路中。[註 14]另一方面SMP包含多個包在其中,NUMA和SMP很相像,但是NUMA使用非單一的內存訪問方式。這些對於一台有着多個CPU的電腦來說是非常重要的,因為每個處理器訪問內存的時間會很快的被SMP分享的模組消耗掉,因些會造成很嚴重的延遲,因為CPU要等待可用的內存.這時NUMA是個不錯的選擇,它可以允許有多個CPU同時存在一台電腦中而且SMP也可以同時實現.SMT有一些不同之處,就是SMT會儘可能的減少CPU處理能力的分佈。TLP的實現實際上和超純量體系結構的實現有些相似,其實上它常常被用在超純量體系結構處理器中,如IBM的POWER5。相比於複製整個CPU,SMT會複製需要的部分來提取指令,加密和分配,就像電腦中的一般的暫存器一樣。因此這樣會使SMT CPU保持處理單位運作的連續,一些通常會提供給處理單位多個指令而且來自不同的軟件線程,這和ILP結構很相似。相比於處理多個指令來自同一個線程,它會同時處理來自不同線程的多個指令。

數據並列

編輯上面提及過的處理器都是一些常數儀器[註 15],而針對向量處理的CPU是較不常見的類型,但它的重要性卻越來越高。事實上,在電腦計算上,向量處理是很常見的。顧名思義,向量處理器能在一個命令週期(one instruction)處理多項數據,這有別於只能在一個命令週期內處理單一數據的常數處理器。這兩種不同處理數據的方法,普遍分別稱為『單指令,多資料』(SIMD)及『單指令,單資料』(SISD)。向量處理器最大的優點就是能夠在同一個命令週期中對不同的工作進行最佳化,例如:求一大堆數據的總和及向量的數量積,更典型的例子就是多媒體應用程式(畫像、影像、及聲音)與及眾多不同總類的科學及工程上的工作。當常數處理器只能針對一組數據於單一命令週期內完全執行提取、解碼、執行和寫回四個階段的同時,向量處理器已能對較大型的數據如相同時間內執行相同動作。當然,這假設了這個應用程式於單一命令週期內對處理器進行多次要求。

大多數早期的向量處理器,例如Cray-1,大多都只會用於和科研及密碼學有關的應用程式。但是,隨着多媒體向數碼媒體轉移,對於能做到『單指令,多資料』的普通用途處理器需求大增。於是,在浮點計數機普及化不久,擁有『單指令,多資料』功能的普通用途處理器便面世了。有些早期的『單指令,多資料』規格,如英特爾的MMX,只能作整數運算。因為大多數要求『單指令,多資料』的應用程式都要處理浮點數碼,所以這個規格對軟件開發者無疑是一個主要障礙。幸好,這些早期的設計慢慢地被改進和重新設計為現時普遍的『單指令,多資料』新規格,AMD公司也推出了第一個真正能執行浮點SIMD指令集3DNow!,在每個時脈週期可得到4個單精確度浮點數結果,是當時一般x87浮點處理器的4倍。新規格通常都於一ISA關連着。近年,一些值得注意的例子一定要數英特爾的SSE和PowerPC相關的AltiVec(亦稱為VMX)。[註 16]

多核心

編輯多核心中央處理器是在中央處理器晶片或封裝中包含多個處理器核心,以偶數為核心數目較為常見,一般共用第二級緩衝記憶體。現今使用雙核心和四核心以上處理器的個人電腦已相當普遍。

第一顆雙核心處理器為IBM POWER4處理器,2012年IBM發佈了最新8核心的POWER 7+處理器,擁有80MB L3緩衝記憶體/晶片。

效能

編輯CPU的效能和速度取決於時鐘頻率(一般以赫茲或十億赫茲計算,即hz與Ghz)和每週期可處理的指令(IPC),兩者合併起來就是每秒可處理的指令(IPS)。[6] IPS值代表了CPU在幾種人工指令序列下「高峰期」的執行率,指示和應用。而現實中CPU組成的混合指令和應用,可能需要比IPS值顯示的,用更長的時間來完成。而內存層次結構的效能也大大影響中央處理器的效能。通常工程師便用各種已標準化的測試去測試CPU的效能,已標準化的測試通常被稱為「基準」(Benchmarks)。如SPECint,此軟仵試圖模擬現實中的環境。測量各常用的應用程式,試圖得出現實中CPU的績效。

提高電腦的處理效能,亦使用多核心處理器。原理基本上是一個集成電路插入兩個以上的個別處理器(意義上稱為核心)[7]。在理想的情況下,雙核心處理器效能將是整塊性核心處理器的兩倍。然而,在現實中,因不完善的軟件演算法,多核心處理器效能增益遠遠低於理論,增益只有50%左右。但增加核心數量的處理器,依然可增加一台計算機可以處理的工作量。這意味着該處理器可以處理大量的不同步的指令和事件,可分擔第一核心不堪重負的工作。有時,第二核心將和相鄰核心同時處理相同的任務,以防止崩潰。

CPU發熱原理

編輯CPU是電腦系統中的核心組件,負責執行各種計算和指令操作。當CPU執行時,它會進行大量的電子計算和數據處理操作,這需要電流通過晶片內部的導線和電晶體進行傳輸和開關操作。這個過程會導致電子之間的摩擦和碰撞,產生能量損耗,進而轉化為熱能。

另外,現代CPU在高效能的同時也具有較高的功耗。當CPU執行時,它會消耗相當的電能,其中一部分會被轉化為熱能。

實際應用

編輯中央處理器大規模應用在個人電腦上,現今電腦可進入家庭。全因集成電路的發展,令PC在大小、效能以及價位等多個方面均有長足的進步。現今中央處理器價錢平宜,用戶可自行組裝個人電腦。主機板等主要電腦元件,均配合中央處理器設計。不同類型的中央處理器安裝到主機板上不同類型的CPU插槽中(如英特爾的LGA 1700、超微半導體的Socket AM5),令中央處理器變得更省電,溫度更低。大多數IBM PC相容機(Pentium以後被稱為「標準PC」(Standard PC))使用x86架構的處理器,他們主要由英特爾和超微半導體兩家公司生産,此外威盛電子也有參與中央處理器的生產。但與IBM PC相容機不同,在2006年之前蘋果電腦所使用的處理器一直是IBM PowerPC RISC,之後的蘋果電腦轉而採用英特爾的處理器,以及EFI韌體。可見中央處理器在現代電腦的重要地位。[來源請求]

著名公司

編輯以下公司曾經或正在生產中央處理器;包含已經倒閉、退出市場或被併購的公司。

- AMD(超微)

- Intel(英特爾)

- Andes (晶心科技)

- ARM(安謀)

- Apple(蘋果)

- Broadcom Limited(博通)

- Cirrus Logic(凌雲邏輯)

- Cyrix(賽瑞克斯)

- 龍芯(中國科學院)

- DEC(迪吉多)

- Fairchild(仙童)

- Fujitsu(富士通)

- Harris(哈瑞斯)

- Hewlett Packard(惠普)

- Hitachi(日立),見Renesas(瑞薩)

- HUAWEI (華為)

- IBM(國際商業機器)

- IDT

- Intersil

- Maxwell(麥克斯韋)

- MHS

- Microsystems International

- MIPS Technologies(美普思科技)

- Mitsubishi(三菱),見Renesas(瑞薩)

- MOS Technology

- Motorola (摩托羅拉)

- MediaTek(聯發科)

- NS(國家半導體)

- NEC(日本電氣),見Renesas(瑞薩)

- NexGen

- OKI(沖電氣)

- OPTi

- Philips(飛利浦)

- Qualcomm(高通)

- RCA(美國無綫電)

- Renesas(瑞薩)

- Rise

- Rockwell(洛克威爾)

- Samsung (三星)

- SGS,見ST(意法半導體)

- Sharp

- ST(意法半導體)

- Siemens(西門子)

- Synertek

- Sun(昇陽)

- Thompson(托馬森)

- Thomson(湯姆遜半導體),見ST(意法半導體)

- TSMC(台積電)

- TI(德克薩斯儀器)

- Toshiba(東芝)

- Transmeta(全美達)

- UMC(聯電)

- VIA(威盛)

- Western Design Center(西部設計中心)

- Western Electric(西部電氣)

- ZiLOG

註釋

編輯- ^ 雖然EDVAC在ENIAC建造之前幾年(2015)就已在設計,ENIAC已在1948年改造成能執行儲存程式的電腦,此時EDVAC正在建造。雖然建造時因費用與時限的關係而將儲存程式功能從ENIAC的藍圖中移除,ENIAC依然早於EDVAC成為第一個儲存程式型電腦。

- ^ 在正常運作時造成的陰極劣化最終將導致真空管停止運作。另外,有時候真空管的封口有缺陷也會加速陰極劣化,請參照真空管。

- ^ 因為程式計數器記錄的是內存地址,而不是指令,所以它的增長取決於指令在內存中所佔的單位數。在固定長度指令ISA中,每個指令所佔用的內存單位是相同的。例如一個32位元的ISA固定長度指令將使用8位元內存單位,而且每次將增加4個PC單位。使用變數長度的ISA指令,如x86,它的PC在內存中的增長量取決於最後一個指令的長度。這裏要注意的是在更複雜的CPU中,最後一個指令的執行不一定會導至PC單位的增長,特別的是在大量數據傳輸和超純量體系結構中。

- ^ 因為CPU指令集的結構是基於它的介面和使用方法,所以它經常用來區別CPU的"種類"。例如一個PowerPC CPU會用到許多不的Power ISA變數。有一些CPU,如英特爾Itanium,可以解譯多個ISA指令;不過這項工作大多由軟件來完成。多於直接將它在硬件中實現。(參見模擬器)

- ^ 一些早期的電腦如馬克一號並不支援任何"jump"指令,因些而限制了程式的複雜性。這理由很大程度上導致它們不被認為是嚴格意義上的CPU,儘管它們和儲存程序電腦相似。

- ^ 這裏的描述事實上是一個簡單的關於經典RISC管線化的介紹。它很大程度上沒有考慮到CPU緩衝記憶體的重要性,因而也少了對數據傳輸訪問的介紹。如果想了解更多資訊請查閱相關資料。

- ^ 物理概念上的電壓是一種模擬值,實際上可能的值可以有無限多種。為了物理上表達二進制數,我們把特定範圍的電壓的值定為1或者是0。電壓的範圍通常是構建CPU的部件的運作參數,例如電晶體的閾值限制,所決定。

- ^ 當CPU的整數精確度範圍被限制的時候,它可以透過軟件和硬件技術相互合作的方法來克服。當我們使用額外的內存時,軟件可以處理比CPU限制大幾個數量級的整數。有時CPU的ISA也會提供相關的指令,幫助軟件更快速地處理大整數。雖然這種處理大整數的方法會比使用擁有高整數精確度的CPU要慢一些,對於處理那些需要大精確度整數的應用,它是一種可取的方法,特別是整數精確度的原生支援成本過高的時候。

- ^ 事實上所有同步運算CPU都運用了序向邏輯電路和組合邏輯電路的結合。(參見布林運算)

- ^ 運用時脈閘控技術的一個最近的設計是基於IBM PowerPC的Xbox 360。它大量利用時脈閘控技術來減少在執行電動遊戲時所需電量的消耗。

- ^ 我們要注意的是不管是ILP或TLP都不可以做為對方的上層控制。它們在增強CPU平行處理能力上有着不同的意義。它們有着各自的優缺點,而且取決於CPU可處理軟件種類。High-TLP CPUs經常被用來處理一些可以很自身份解成許多小程式的軟件中.因而稱它為"embarrassingly parallel problems." 因此high TLP設計方法可以連續快速的處理一些運算問題,比如SMP會使用太多的時間來處理ILP裝置(超純量體系結構的CPU),反之亦然。

- ^ 最佳(或最高)IPC率在超純量體系結構中是很難保持不變的,它可能導致使傳輸總是失敗.因此在高超純量體系CPU中,平均相同IPC的方法的使用,多於最佳(或最高)IPC的使用.

- ^ 儘管SMP和NUMA都是在系統層中的TLP設計方案,但它們還是需要CPU在設計中的支援.

- ^ 因TPL的使用比ILP時間更長,所以晶片層多處理技術或多或少的只可以在以後的基於集成電路的微處理器。集成電路多處理技術中看到。導至這種情況的原因是,它不在適和早期的分立元件裝置,而且也只被運用了幾年(1990-2000),如今注意力都集中在設計高運算能力的CPU,這些CPU都運用了超純量結構的IPC設計方案,如英特爾Pentium 4。儘管如此,以前的技術似乎又被運用到現在CPU設計中來,又換回到稍底層的High -TLP傳輸中。它表現在增值雙核或多核CMP的設計中,如英特爾最新的設計中少了一些超純量體系結構的設計p6,之後的CPU多運用了CMP,包括x86-64、Opteron和Athlon 64 x2,還有Sparc UltraSparc T1,IBM Power4和Power5。還有一些其它的電動遊戲機的CPU,如x360中的三核PowerPC設計。

- ^ 早期scalar被用來比較不同ILP方案的IPC(instructions per cycle)的間隔數量。在這裏它表示數學中用來比較向量大小的一個概念。

- ^ 雖然在英特爾的主流CPU中,MMX已經被SSE/SSE2/SSE3所取代,但在之後的CPU中仍然支援MMX技術,通常使用擁有豐富的SSE指令集的相同的硬件來提供大部分的MMX功能。

參考文獻

編輯- ^ First Draft of a Report on the EDVAC (PDF). Moore School of Electrical Engineering, University of Pennsylvania. 1945 [2022-07-02]. (原始內容存檔 (PDF)於2021-03-09).

- ^ Weik, Martin H. A Third Survey of Domestic Electronic Digital Computing Systems. Ballistic Research Laboratory. 1961 [2006-03-16]. (原始內容存檔於2017-09-11).

- ^ 3.0 3.1 Amdahl, G. M.; Blaauw, G. A.; Brooks, F. P. Jr. Architecture of the IBM System/360. IBM Journal of Research and Development (IBM). April 1964, 8 (2): 87–101. ISSN 0018-8646. doi:10.1147/rd.82.0087.

- ^ LSI-11 Module Descriptions (PDF). LSI-11, PDP-11/03 user's manual 2nd. Maynard, Massachusetts: Digital Equipment Corporation. November 1975: 4–3 [2022-07-02]. (原始內容存檔 (PDF)於2021-10-10).

- ^ Garside, J. D.; Furber, S. B.; Chung, S-H. AMULET3 Revealed. University of Manchester Computer Science Department. 1999. (原始內容存檔於December 10, 2005).

- ^ "CPU Frequency". CPU World Glossary. CPU World. 25 March 2008. Retrieved 1 January 2010.

- ^ "What is (a) multi-core processor?". Data Center Definitions. SearchDataCenter.com. 27 March 2007. Retrieved 1 January 2010.

外部連結

編輯- CPU簡史

- CPU歷史上的十個第一

- CMP簡要介紹 (頁面存檔備份,存於互聯網檔案館) - 簡要的介紹了片上多核處理器,對常見的片上多核處理器採用的技術進行了綜述

- Processor Design: An Introduction - 詳盡地介紹微處理器的設計,雖然有些資料未完成和落伍,但仍具參考價值。

- 微處理器如何運作(頁面存檔備份,存於互聯網檔案館)

- Pipelining: An Overview (頁面存檔備份,存於互聯網檔案館) - CPU管線化技術的簡介,由Ars Technica成員所寫。

- SIMD Architectures (頁面存檔備份,存於互聯網檔案館) - SIMD的介紹與說明,尤其着重於SIMD與桌上電腦的關係。一樣由Ars Technica所寫。

- 微處理器生產商

- Advanced Micro Devices(頁面存檔備份,存於互聯網檔案館) - AMD,其中一個生產相容x86電腦的CPU生產商

- ARM Ltd(頁面存檔備份,存於互聯網檔案館) - 安謀國際科技,少數隻授權其CPU設計而沒有自行製造的公司。嵌入式應用軟件最常被ARM架構微處理器執行。

- Freescale Semiconductor(頁面存檔備份,存於互聯網檔案館) -(前身是Motorola的)飛思卡爾,設計數款嵌入裝置以及SoC PowerPC處理器。

- IBM Microelectronics - IBM的微電子分公司,設計出許多IBM POWER與PowerPC,包括許多電視遊樂器的CPU。

- Intel Corp(頁面存檔備份,存於互聯網檔案館) - 英特爾,許多著名CPU的生產者,包括IA-32、IA-64與XScale。也是許多用在他們自家CPU的週邊產品的製造者。

- MIPS Technologies(頁面存檔備份,存於互聯網檔案館) - MIPS科技公司,MIPS架構的製造者,在RISC設計領域的先鋒。

- Sun Microsystems(頁面存檔備份,存於互聯網檔案館) - 昇陽,SPARC架構(RISC)的製造者。

- Transmeta(頁面存檔備份,存於互聯網檔案館) - 全美達,低電力X86相容CPU的創造者,例如Crusoe與Efficeon。

- VIA(頁面存檔備份,存於互聯網檔案館) - 威盛,低功率X86相容CPU的製造商,例如C3。

參見

編輯